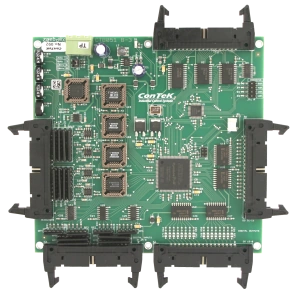

XmPga02 - Modul programovatelných vstupů a výstupů

- nahrazuje modul XmPga01

- připojení na rozhraní XBus řídicího systému

- adresní prostor 16 bajtů

- 16 digitálních vstupů

- nastavitelná úroveň vstupního napětí pro čtveřice signálů (5V, 24V)

- 32 digitálních výstupů

- 16 výstupů TTL

- 16 výstupů TTL, 0-5V PWM nebo s tranzistorovými spínači

- oscilátor pro buzení resolverů

- nastavitelná frekvence 2, 5, 10, 20kHz

- až 4 resolverové vstupy

- rozlišení 12 bit

- inkrementální i absolutní mód

- nastavitelná citlivost vstupů

- obsluha všech vstupů a výstupů FPGA obvodem

- variabilní funkce, dáno návrhem obsahu FPGA

- 14976 bajtů RAM pro obecné použití

- základní hodinový kmitočet 20MHz

- 2x PLL (násobení, dělení, fázový posuv)

Popis

XmPga02 je modul určená pro aplikace, kde je potřeba pracovat s rotačními nebo lineárními resolvery nebo zvláštním způsobem obsluhovat digitální vstupy/výstupy nebo analogové výstupy. Modulem lze např. realizovat rychlé řízení krokových motorů s MSM01c, generování sekvencí digitálních signálů, přesné měření frekvence nebo střídy digitálního signálu, čítače impulsů apod.

Ve spojení se servopohony je modul vhodný pro vytváření vzájemně synchronizovaných elektronických vaček v jejich nejsložitějších podobách.

Modul se připojuje na rozhraní XBus řídicího systému ConTeK.

Základem modulu je programovatelné pole FPGA Altera, které zajišťuje obsluhu všech digitálních vstupů, výstupů a dekodérů resolverů. Funkce FPGA je dána konfiguračním souborem, který je nahráván z řídicí jednotky prostřednictvím sběrnice XBus.

Resolverové vstupy umožňují připojení a obsluhu až 4 rotačních nebo lineárních resolverů. Vstupy jsou tvořeny zesilovačem s nastavitelným zesílením, které se provádí výměnou odporových sítí osazených v patici. Zesílení se nastavuje vždy pro 2 vstupy společně. Nestejnoměrnost vstupních signálů lze kompenzovat odporovými trimry.

Buzení všech resolverů zajišťuje jeden společný sinusový oscilátor s nastavitelnou frekvencí.

Digitální vstupy jsou tvořeny odporovými T-články, které umožňují nastavení úrovně vstupního signálu. Nastavení úrovně se provádí výměnou odporové sítě osazené v patici, která je společná vždy pro čtveřici signálů.

Digitální výstupy jsou tvořeny budiči TTL. Až 16 výstupů může být osazeno tranzistorovými spínači nebo RC filtry pro generování analogového napětí 0-5V pomocí PWM.

Technické parametry

- Napájení: 5V ze sběrnice XBus

- Spotřeba: 220mA (bez resolverů)

- Pracovní teplota: 0-70°C

- Připojení

- Sběrnice: ConTeK XBus, 34 pin

- Adresace: nastavitelná v rozsahu 00h-F0h po krocích 16 bajtů

- Přerušení: IRQB

- Rychlost: dle projektu FPGA

- Digitální vstupy

- Počet: 16

- Vstupní napětí: nastavitelné ve skupinách po 4 vstupech, 24V nebo 5V

- Úroveň L: max. 8V pro 24V rozsah, 1,6V pro 5V rozsah

- Úroveň H: min. 16V pro 24V rozsah, 3,3V pro 5V rozsah

- Digitální výstupy TTL

- Počet: 16

- Výstupní napětí: 5V

- Úroveň L: max. 0,33V při 6mA

- Úroveň H: min. 3,7V při -6mA

- Frekvence: dle projektu FPGA

- Digitální výstupy TTL/tranzistorový spínač/analog 0-5V

- Typ: tranzistorový spínač

- Počet: 8 nebo 16

- Výstupní napětí: max. 35V

- Výstupní proud: max. 100mA

- Úbytek napětí: 1,5V

- Frekvence: max. 100kHz

- Typ: TTL

- Počet: 1-16

- Výstupní napětí: 5V

- Úroveň L: max. 0,33V při 6mA

- Úroveň H: min. 3,7V při -6mA

- Frekvence: dle projektu FPGA

- Typ: Analogový výstup 0-5V

- Počet: 1-16

- Výstupní napětí: 0-5V

- Rozlišení: dle projektu FPGA

- Frekvence: dle projektu FPGA

- Resolverové vstupy

- Počet: 0-4

- Buzení: napěťové 2,2Vef

- Frekvence buzení: 2, 5, 10, 20kHz

- Vstupní napětí: 2Vef, nastavitelné

- Rychlost: max. 500 ot/s